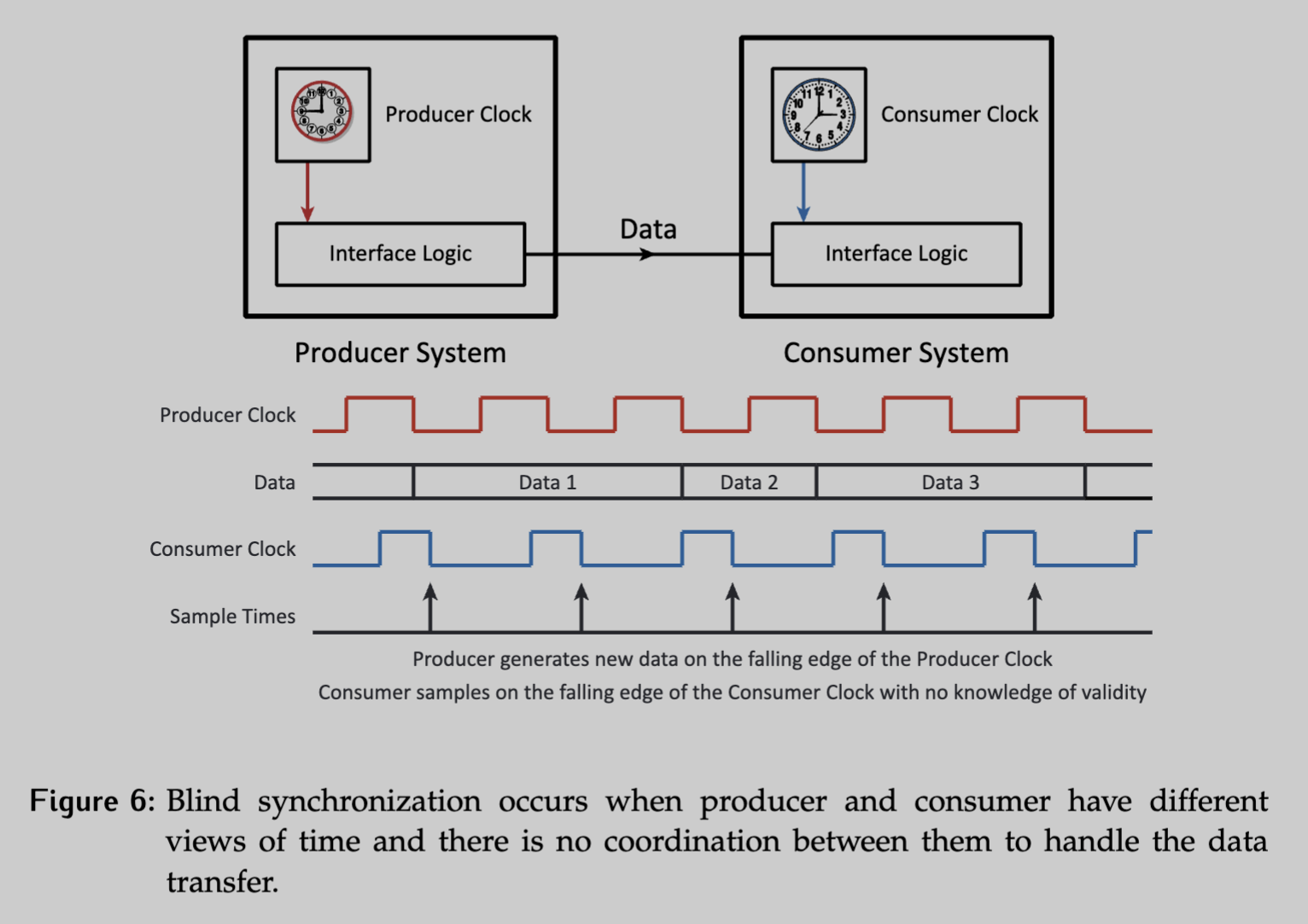

Blind

In the case of blind synchronization, both the producer and consumer have their own internal clocks. This is seen when blind cycle synchronization is used for synchronization at the second level.

- Only data is shared between them, meaning there is no phase synchronization. They could also be operating at very different frequencies.

- The consumer reads the data at its convenience – this could be according to its internal clock as illustrated or based on some other internal timing mechanism.

- Since there’s no synchronization, data could be sampled twice (see Data 1 and Data 3).

- Data could also be completely missed if the consumer did not sample soon enough

- The consumer could sample while the producer is changing the data, leading to a corrupt reading

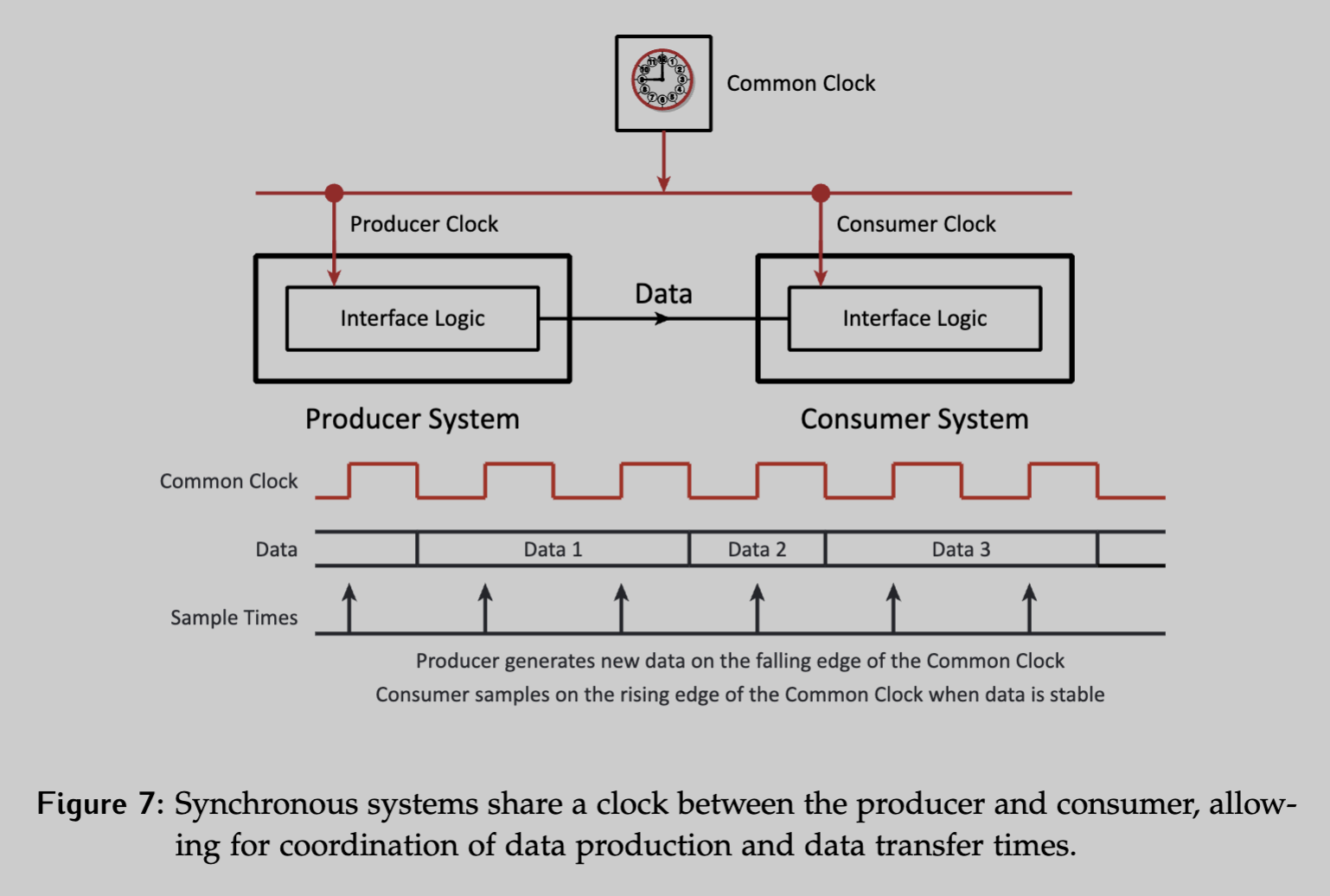

Synchronous

In the asynchronous case, a clock is shared by both sides. It could be generated by the producer, consumer, or be a completely separate piece of hardware. The common view of time makes it simple for the producer and consumer to coordinate.

- For example, the producer may change data on the falling edge of the clock while the consumer reads data on the rising edge.

- There is no possibility of reading data while it is being updated in this case.

There are still some problems:

- What if the producer doesn’t have new data every cycle? The consumer might read the same piece twice.

- How can we tell the difference between a piece of data that hasn’t updated and two sequential data pieces with the same value?

- Does it matter if we read the same piece twice?

The answers to these are dependent on the nature of the system and the data.

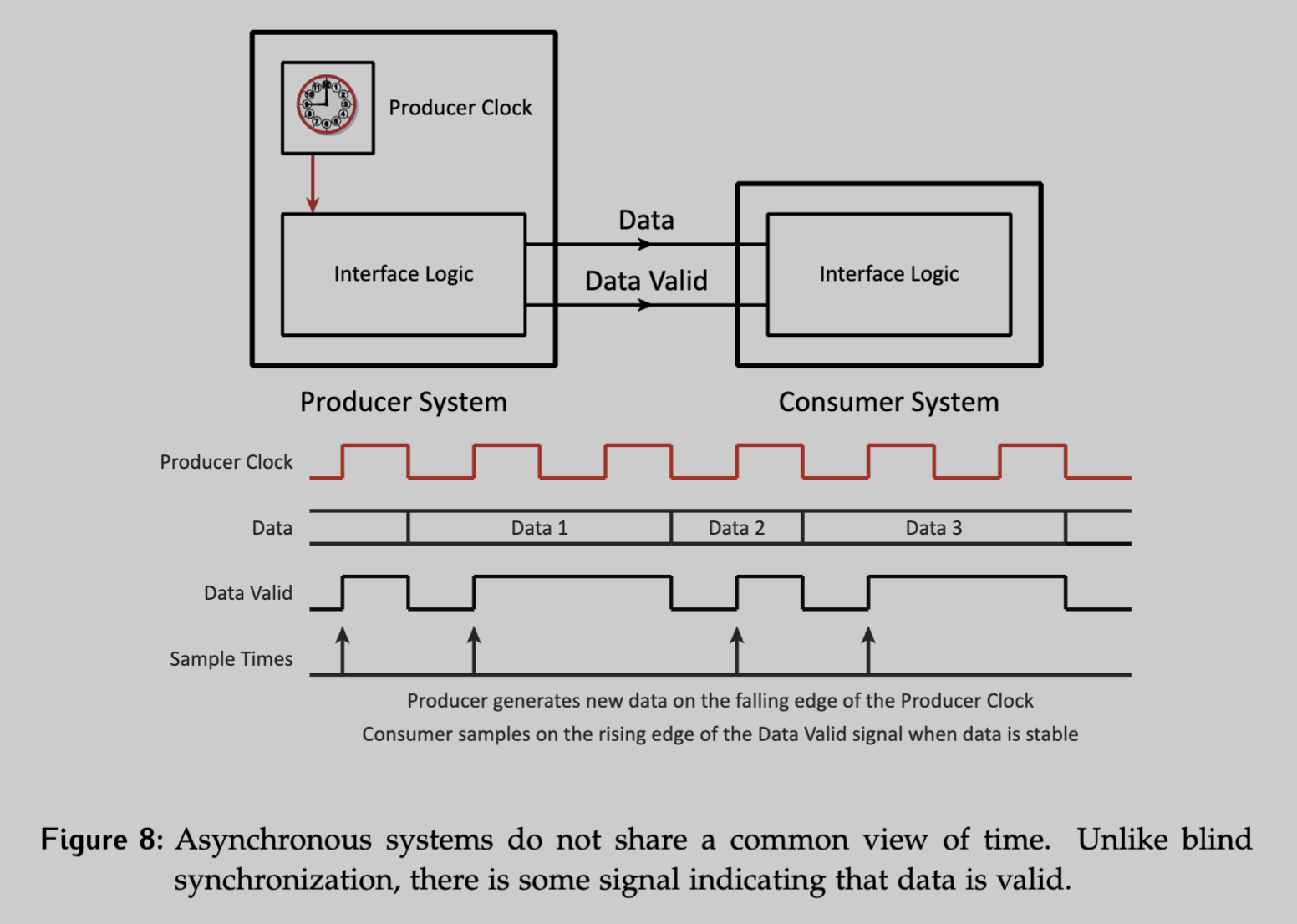

Asynchronous

In the asynchronous case, the two sides do not share a common view of time. Unlike blind synchronization, information is shared between the two sides to indicate when the data is valid.

- In the simplest case, a control signal called data valid could be shared between the two sides. The producer might update data on the falling edge of its internal clock, and set the data valid signal high when new data is available and there is a rising edge on its internal clock.

- Notice that the use of the data valid signal means that data will only be sampled once, and will never be missed